作者: Ken C

这篇文章将探讨两个问题:1) 如何选择释放缓冲器延迟 (RBD) 以确保一个确定性延迟; 2) 如何测量和验证预期的确定性延迟。

选择合适的 RBD 数值

如我前一篇帖子所讨论的那样,RBD = K 是默认设置。这允许初始线道对齐序列对齐所有的线道,并在随后的多帧边界上释放它们。可能会存在这样的情况,即系统延迟有可能致使最后到达的线道跨越数据释放点。在此情况下,线道的释放或许有一个延迟,该延迟的变化幅度为一个多帧周期,具体数值取决于最后一个到达的线道是恰好在多帧边界之前还是之后。这时,RBD 的选择对于提供足够的裕度以补偿系统延迟中的变化、同时最大限度地减少释放数据时的延迟而言是至关紧要的。

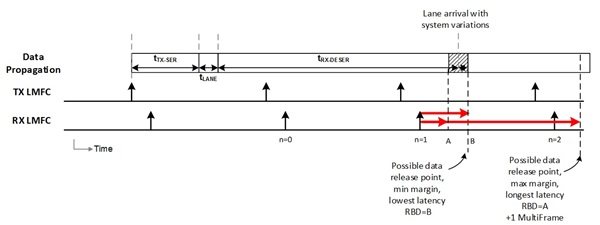

图 1:可能的释放点 A:最大裕度、最大延迟与 B:最小裕度、最小延迟之间的关系

如图 1 中所示,RBD = A 的设置将提供可行的释放点,这些释放点将最大限度地增大针对系统延迟变化的裕度。不过,这也意味着数据必须延迟更久之后再释放,从而导致了更长的延迟。RBD = B 的设置将在最后一个线道到达之后立即释放数据,但是需要谨慎操作以确保所选的延迟可提供足够的裕度,从而避免可能发生有关系统变化的问题。

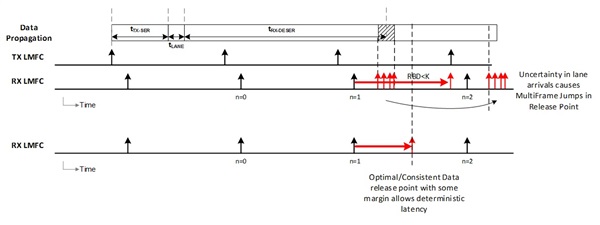

图 2:调整 RBD 以找到一个可行的最优释放点

有一种可行的设置是使释放点偏移,偏移量是最新到达线道之后的预期系统变化量。这可以在延迟和裕度之间提供适当的平衡以吸收可能的系统变化。这个最优的数据释放点可从系统参数(如果它们是现成的话)推导而出。对于延迟参数并非现成可用的场合,您可以凭借经验来推导数据释放点。

首先,从采用默认的 RBD = K 设置开始;然后,重复供电循环并调整延迟,直到在实测延迟中观察到完整的多帧跳跃为止。这是最后一个线道到达的上限。当由系统变化引起的延迟继续减小 RBD 值时,延迟将实现稳定。这是最后一个线道到达的下限。上限与下限之间的差异即为系统延迟变化。把 RBD 延迟设定在上限的这个偏移值是一种可能的最优解决方案,其将提供针对系统变化的裕度,同时提供一个恒定的数据释放点。

计算、测量和验证确定性延迟

采用一个由 16 位、370 MSPS ADC16DX370 和一个 FPGA 组成的系统来把实测延迟与我们计算所得的预期延迟进行比较。ADC16DX370 连接至 FPGA 平台的 FPGA 夹层卡 (FMC) 端口。生成一个脉冲并馈入模数转换器 (ADC) 的输入,以及一个示波器。ADC 对输入信号进行采样,并通过 JESD204B 链路把该数据传递至 FPGA。一旦接收到 ADC 采样,FPGA 随后即把最高有效位 (MSB) 发送至一个将由示波器监察的输入 / 输出 (I/O) 引脚。通过把电缆和电路板印制线的延迟、以及对输入脉冲信号进行采样并通过链路传递至 FPGA 所需的时间考虑在内,即可测量并确认延迟。

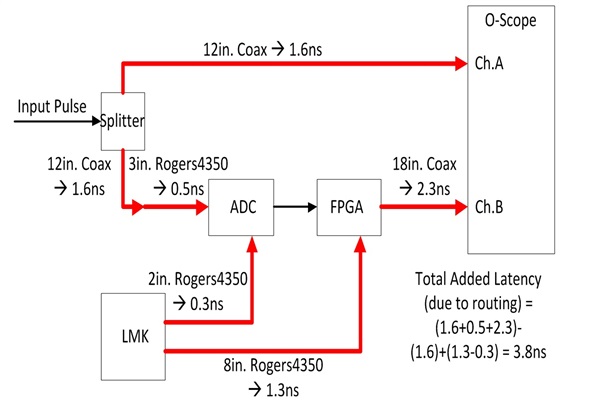

图 3 中的方框图示出了针对该设置不同部分的电缆和印制线预期延迟。

图 3:在延迟计算中使用的其他非器件相关延迟。一个脉冲被发送至示波器和 ADC。将捕获之采样的 MSB 与该脉冲进行比较以测量延迟。

在 ADC16DX370 和 FPGA 上采用了下面的配置:

1. ADC 器件时钟 = 370MSPS (2.7ns 周期)。

2. JESD204B 参数:

a. L = 4,M = 2,F = 1,S = 1,K = 32。

b. 帧周期 = 10*F/线路速率 = 10*1/3700MSPS = 2.7ns。

c. LMFC 周期 = 帧周期* K = 2.7ns*32 = 86.4ns。

3. FPGA 器件时钟 = 92.5MHz (10.8ns)。

4. 链路参数(帧周期):

a. .

b. N = 2,RBD = 28(小于 K)。

5. 链路延迟以外的其他延迟(帧周期):

a. ADC 内核延迟 = 12.5。

b. DEVCLK 路由时滞和 MSB 输出电缆 / 印刷电路板 (PCB) 路由延迟 = 3.8ns/2.7ns ~ 1.4。

c. ADC 内部的 SYSREF/DEVCLK 采样时滞 = 1.5。

d. 用于锁存样本和发出 MSB 的 FPGA 接收器处理延迟 = ~7。

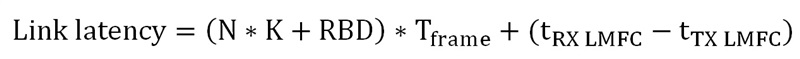

如我在前一篇帖子中推导的那样,(1) 式为:

链路延迟 = (N * K + RBD) * Tframe + (tRX LMFC - tTX LMFC)

链路延迟 = 116.5 个帧周期

估算的总延迟 = 链路延迟 + 其他延迟 = 116.5 + 12.5 + 1.4 + 1.5 + 7 = 138.9 个周期

该延迟是在介于信号脉冲和取自 FPGA 的 MSB 之间的多个电源周期中测量的。

这里给出了一个 379.6ns 的固定延迟结果,等于 140.4 个帧周期。这与根据系统参数估算的 139 个周期的延迟十分吻合。

如需获取有关采用 JESD204B 之设计的其他建议,请查看以下的资源:

· 在此次培训演示中更深入地探讨 JESD204B 子类和确定性延迟。

· 下载我们的 JESD204B 白皮书,以此您可以在过渡到使用 JESD204B 时,获得关于必要知识的相关小贴士。

· 阅读更多的 JESD204B 博客。

· 了解 TI 的 JESD204B ADC、DAC、时钟和工具。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。