作者:Bosheng Sun

作为德州仪器 (TI) 高性能隔离式电源团队的一名工程师,我主要与通常需要高性能电源的服务器及电信公司合作。开发高端功率因数校正 (PFC) 设计,不仅需要在特定负载下使总谐波失真 (THD) 低于一定百分比,而且还需要每个谐波都不超过 IEC 61000-3-2 合规性标准中规定的特定限值。在这篇共分两部分的博客中,我将介绍用于降低 PFC 谐波和改善 THD 的谐波注入法。

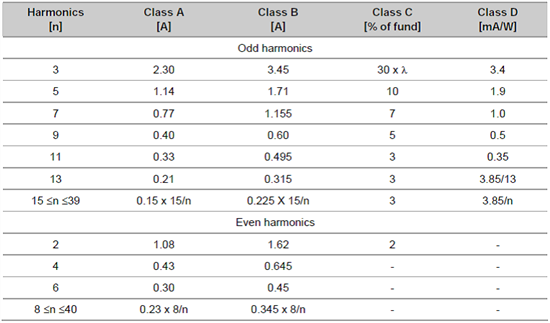

表 1,IEC 61000-3-2 谐波限值

闭环调谐通常是一种降低谐波失真、改善 THD 的有效方法。不过,我看到过有 PFC 设计通过了 THD 测试,但无论工程师如何努力调谐控制环路,也无法通过单个谐波失真测试。传统闭环调谐在这种情况下帮助不大。因此需要使用新的方法来应对单个谐波。

我看到过工程师通过在单开关三相位整流器设计中注入三阶电流信号来降低 THD。这使我想到了一种抑制(补偿)高幅值谐波的类似方法。这种方法应该很容易使用,不仅不涉及额外的硬件成本,而且还非常灵活,可抑制任何阶数的谐波。

在 TI UCD3138 等数字电源控制器的帮助下,我开发出了一种简单的谐波注入法,其可有效抑制(补偿)任意阶数的谐波。因此,可降低特定阶数的谐波幅值、改善 THD。

基本原理是生成一个特定阶数的正弦信号,并将该信号注入 PFC 电流控制环路。正弦信号的幅值可根据负载和输入电压等工作条件进行动态调整,从而可最大限度地提高抑制效果。

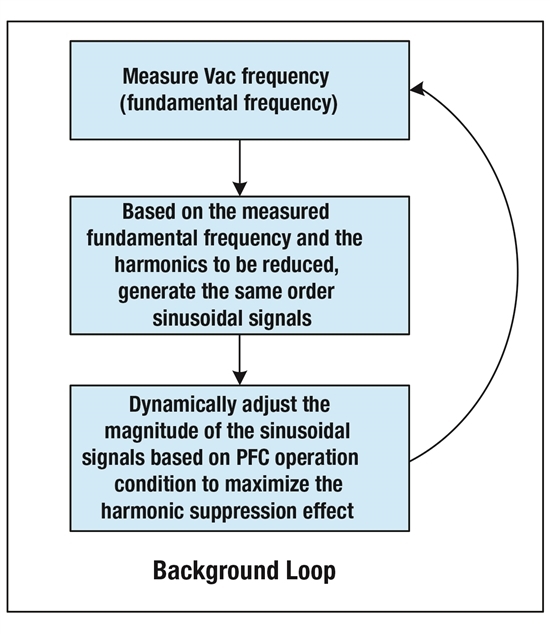

更具体说,在数字控制 PFC 中,固件分为两个主环路:针对低优先级和低速任务(例如内务操作)的后台环路;以及针对高优先级和时间紧迫型任务(例如 PFC 状态机)的中断环路。

按照以下步骤在后台环路中实施该方法:

该过程演示如下:

图 1:后台环路中的谐波注入流程图

相关博客:

原文请参见: http://e2e.ti.com/blogs_/b/powerhouse/archive/2014/05/23/how-to-reduce-pfc-harmonics-and-improve-thd-using-harmonic-injection-part-1.aspx

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。